# HIGH-SPEED DIGITAL DESIGN

# A Handbook of Black Magic

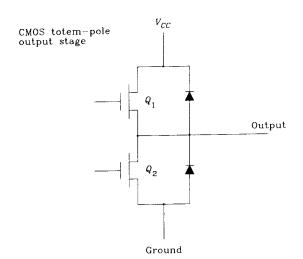

## HOWARD W. JOHNSON, PH.D.

Olympic Technology Group, Inc.

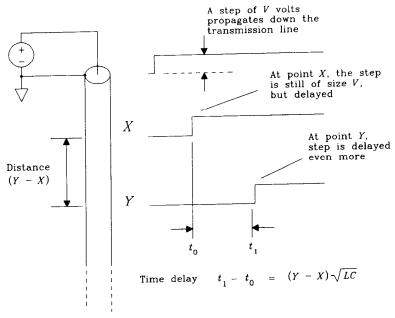

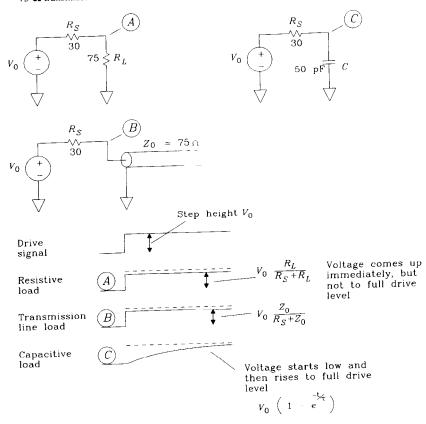

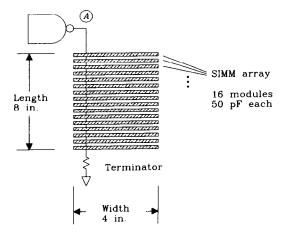

#### MARTIN GRAHAM, PH.D.

University of California at Berkeley

http://www.prenhall.com

# Contents

| Preface ix                                                                                                                                                                                                                                                                                                                      |

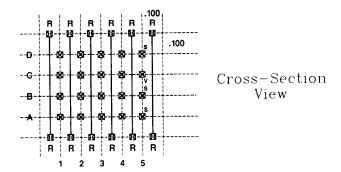

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fundamentals 1                                                                                                                                                                                                                                                                                                                  |

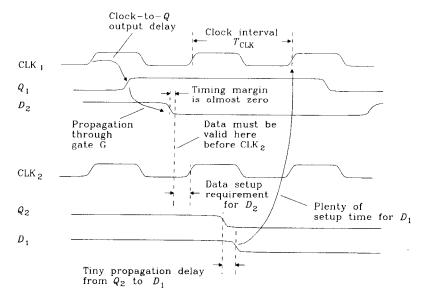

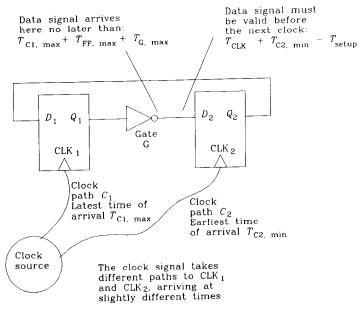

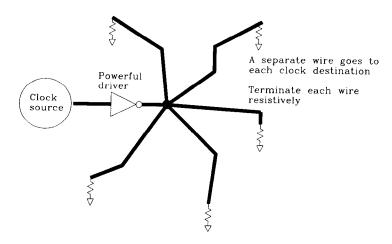

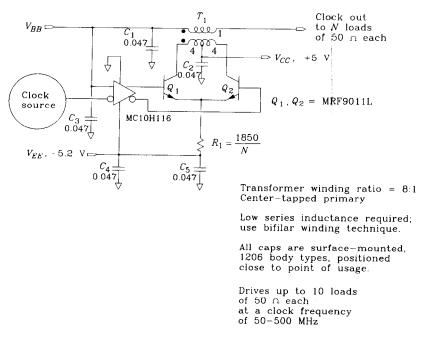

| 1.1 Frequency and Time 1 1.2 Time and Distance 6 1.3 Lumped Versus Distributed Systems 7 1.4 A Note About 3 dB and RMS Frequencies 8 1.5 Four Kinds of Reactance 10 1.6 Ordinary Capacitance 11 1.7 Ordinary Inductance 17 1.8 A Better Method for Estimating Decay Time 22 1.9 Mutual Capacitance 25 1.10 Mutual Inductance 29 |

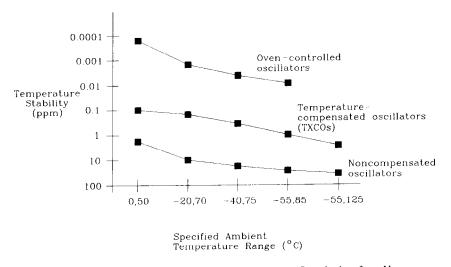

| High-Speed Properties of Logic Gates 37                                                                                                                                                                                                                                                                                         |

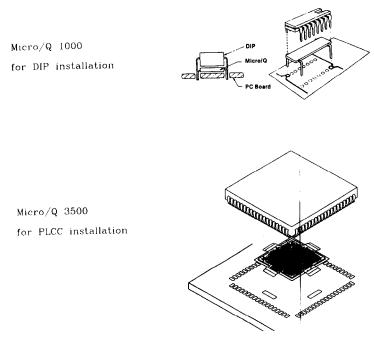

| <ul> <li>2.1 Historical Development of a Very Old Digital Technology 37</li> <li>2.2 Power 39</li> <li>2.3 Speed 59</li> <li>2.4 Packaging 66</li> </ul>                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                 |

vi Contents

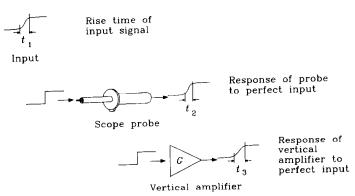

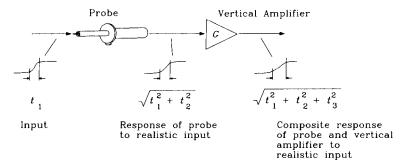

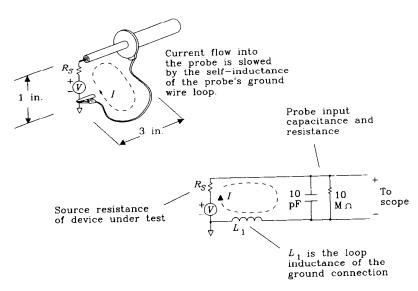

| 3 | Measurement Techniques 83                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

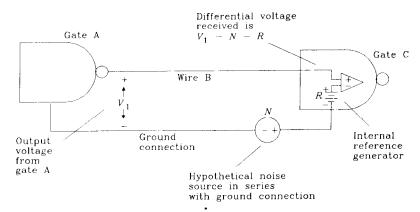

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

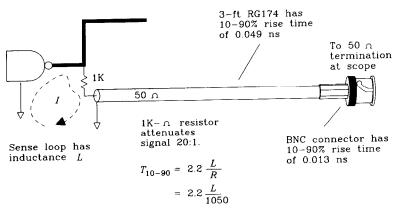

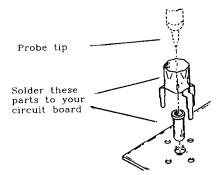

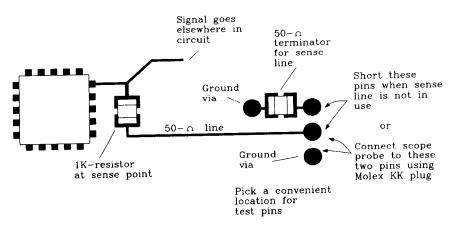

|   | 3.1 Rise Time and Bandwidth of Oscilloscope Probes 83 3.2 Self-inductance of a Probe Ground Loop 86 3.3 Spurious Signal Pickup from Probe Ground Loops 92 3.4 How Probes Load Down a Circuit 95 3.5 Special Probing Fixtures 98 3.6 Avoiding Pickup from Probe Shield Currents 104 3.7 Viewing a Serial Data Transmission System 108 3.8 Slowing Down the System Clock 110 3.9 Observing Crosstalk 111 3.10 Measuring Operating Margins 113 3.11 Observing Metastable States 120 |   |

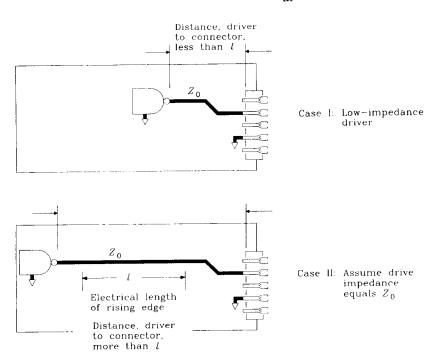

| 4 | Transmission Lines 133                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|   | <ul> <li>4.1 Shortcomings of Ordinary Point-to-Point Wiring</li> <li>4.2 Infinite Uniform Transmission Line</li> <li>4.3 Effects of Source and Load Impedance</li> <li>4.4 Special Transmission Line Cases</li> <li>4.5 Line Impedance and Propagation Delay</li> <li>178</li> </ul>                                                                                                                                                                                             |   |

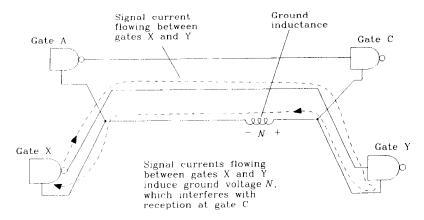

| 5 | Ground Planes and Layer Stacking 189                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

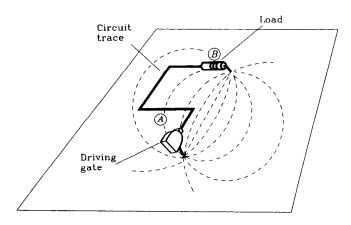

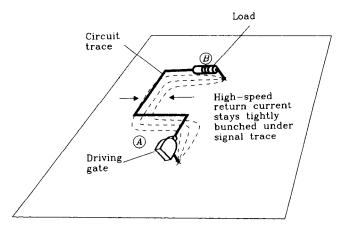

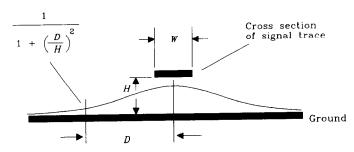

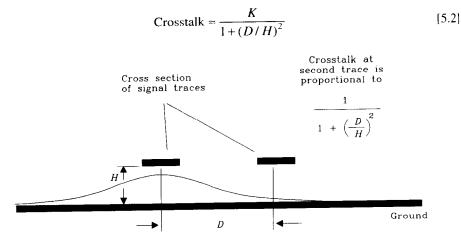

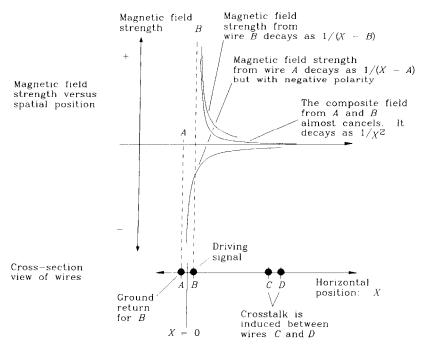

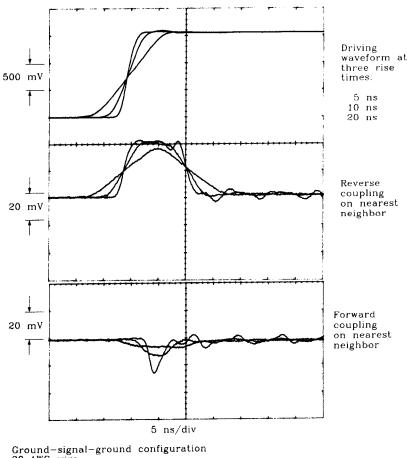

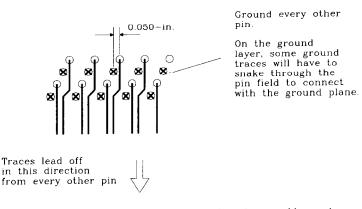

|   | <ul> <li>5.1 High-Speed Current Follows the Path of Least Inductance</li> <li>5.2 Crosstalk in Solid Ground Planes 191</li> <li>5.3 Crosstalk in Slotted Ground Planes 194</li> <li>5.4 Crosstalk in Cross-Hatched Ground Planes 197</li> <li>5.5 Crosstalk with Power and Ground Fingers 199</li> <li>5.6 Guard Traces 201</li> <li>5.7 Near-End and Far-End Crosstalk 204</li> <li>5.8 How to Stack Printed Circuit Board Layers 212</li> </ul>                                | • |

| 6 | Terminations 223                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

|   | <ul> <li>6.1 End Terminators 223</li> <li>6.2 Source Terminators 231</li> <li>6.3 Middle Terminators 235</li> <li>6.4 AC Biasing for End Terminators 236</li> <li>6.5 Resistor Selection 239</li> <li>6.6 Crosstalk in Terminators 244</li> </ul>                                                                                                                                                                                                                                |   |

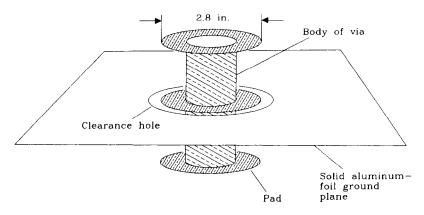

| 7 | Vias 249                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

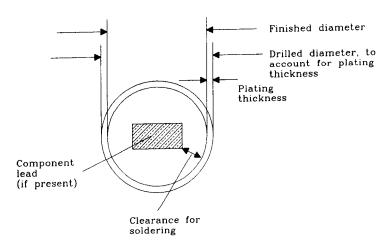

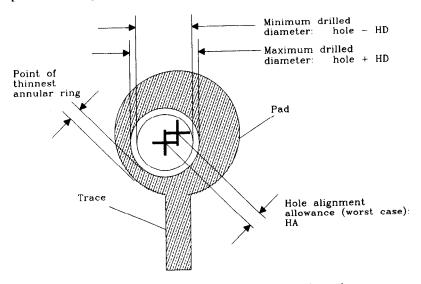

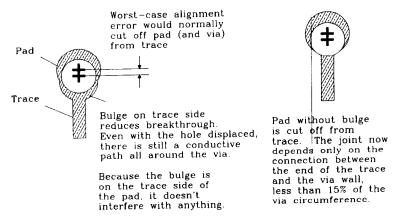

|   | <ul> <li>7.1 Mechanical Properties of Vias 249</li> <li>7.2 Capacitance of Vias 257</li> <li>7.3 Inductance of Vias 258</li> <li>7.4 Return Current and Its Relation to Vias 260</li> </ul>                                                                                                                                                                                                                                                                                      |   |

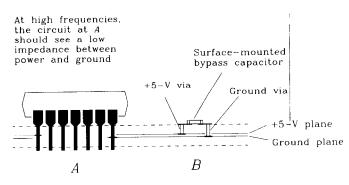

| 8  | Power Systems 263                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|    | <ul> <li>8.1 Providing a Stable Voltage Reference</li> <li>8.2 Distributing Uniform Voltage 268</li> <li>8.3 Everyday Distribution Problems 279</li> <li>8.4 Choosing a Bypass Capacitor 281</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 263                                                                      |

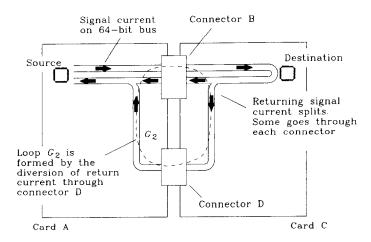

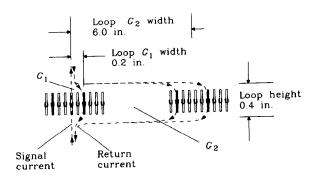

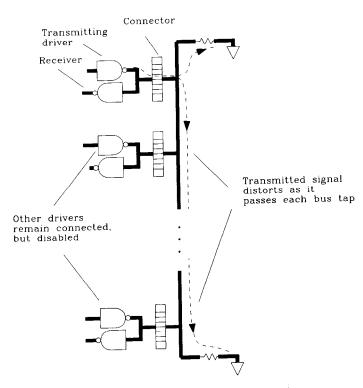

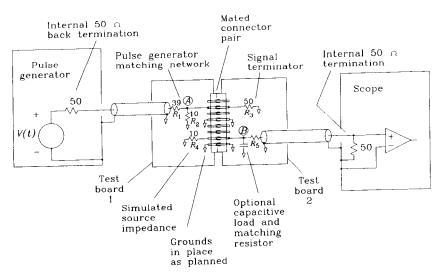

| 9  | Connectors 295                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          |

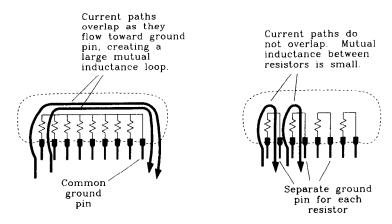

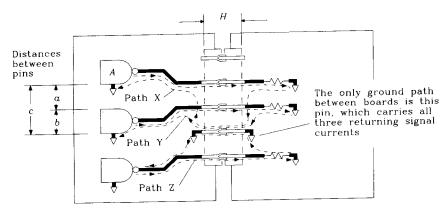

|    | <ul> <li>9.1 Mutual Inductance—How Connectors C Crosstalk 295</li> <li>9.2 Series Inductance—How Connectors Crossitic Capacitance—Using Connector Multidrop Bus 305</li> <li>9.4 Measuring Coupling in a Connector Continuity of Ground Underneath a Consideration Fixing EMI Problems with External Consideration Special Connectors for High-Speed App.</li> <li>9.8 Differential Signaling Through a Connector Connectors of Connectors and Connectors of C</li></ul> | eate EMI 300 rs on a  309 nector 312 nections 314 lications 316 etor 319 |

|    | 9.9 Power Handling Features of Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 321                                                                      |

| 10 | Ribbon Cables 323                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          |

|    | <ul> <li>10.1 Ribbon Cable Signal Propagation</li> <li>10.2 Ribbon Cable Crosstalk</li> <li>10.3 Ribbon Cable Connectors</li> <li>10.4 Ribbon Cable EMI</li> <li>338</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                        |

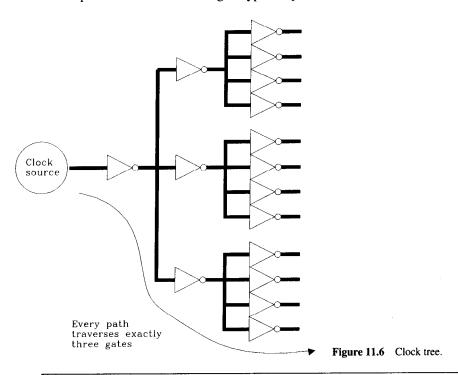

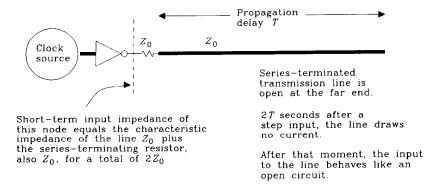

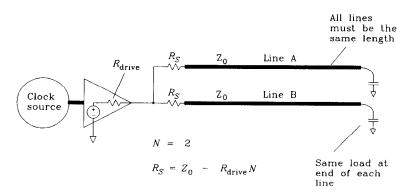

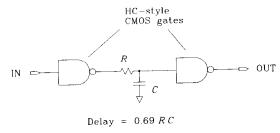

| 11 | Clock Distribution 341                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                          |

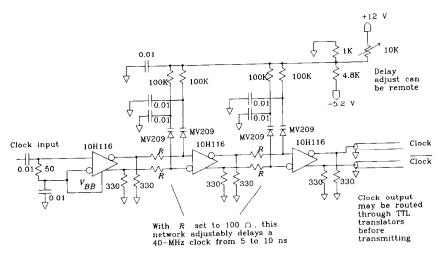

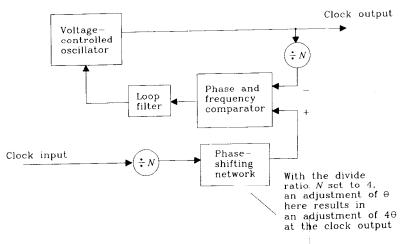

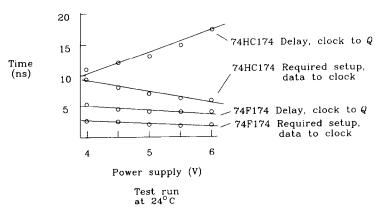

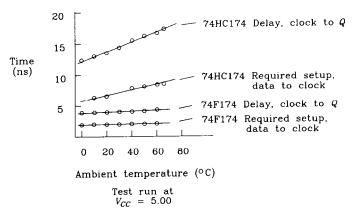

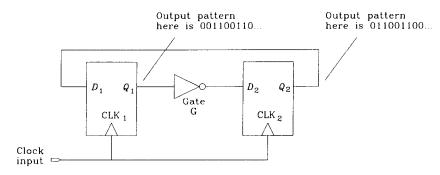

|    | 11.1 Timing Margin 341 11.2 Clock Skew 343 11.3 Using Low-Impedance Drivers 346 11.4 Using Low-Impedance Clock Distributio 11.5 Source Termination of Multiple Clock Li 11.6 Controlling Crosstalk on Clock Lines 11.7 Delay Adjustments 353 11.8 Differential Distribution 360 11.9 Clock Signal Duty Cycle 361 11.10 Canceling Parasitic Capacitance of a Clo Repeater 362 11.11 Decoupling Clock Receivers from the Cl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ines 350<br>352<br>ck                                                    |

| 12 | Clock Oscillators 367                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                          |

|    | 12.1 Using Canned Clock Oscillators 367<br>12.2 Clock Jitter 376                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                                                        |

Collected References 385

A Points to Remember 389

B Calculation of Rise Time 399

C MathCad Formulas 409

Index 441

# Preface

This is a book for digital designers. It highlights and explains analog circuit principles relevant to high-speed digital design. Teaching by example, the authors cover ringing, crosstalk, and radiated noise problems which commonly beset high-speed digital machines.

None of this material is new. On the contrary, it has been handed down by word of mouth and passed along through application notes for many years. This book simply collects together that wisdom. Because much of this material is not covered in standard college curricula, many practicing engineers view high-speed effects as somewhat mysterious, ominous, or daunting. For them, this subject matter has earned the name "black magic." The authors would like to dispel the popular myth that anything unusual or unexplained happens at high speeds. It's simply a matter of knowing which principles apply, and how.

Digital designers working at low speeds do not need this material. In low-speed designs, signals remain clean and well behaved, conforming nicely to the binary model.

At high speeds, where fast signal rise times exaggerate the influence of analog effects, engineers experience a completely different view of logic signals. To them, logic signals often appear hairy, jagged, and distorted. For their products to function, high-speed designers must know and use analog principles. This book explains what those principles are and how to apply them.

X Preface

Readers without the benefit of formal training in analog circuit theory can use and apply the formulas and examples in this book. Readers who have completed a first year class in introductory linear circuit theory may comprehend this material at a deeper level.

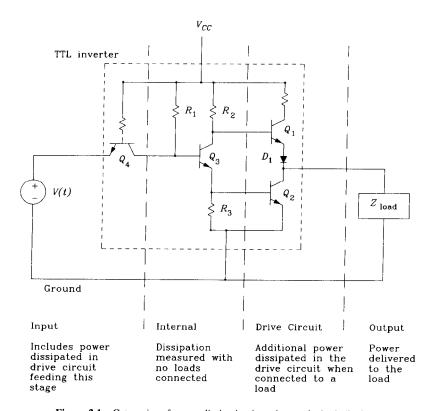

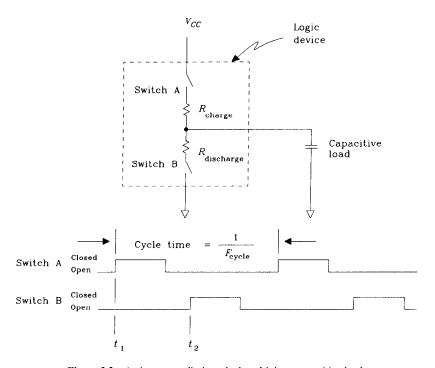

Chapters 1–3 introduce analog circuit terminology, the high-speed properties of logic gates, and standard high-speed measurement techniques, respectively. These three chapters form the core of the book and should be included in any serious study of high-speed logic design.

The remaining chapters, 4–12, each treat specialized topics in high-speed logic design and may be studied in any order.

Appendix A collects highlights from each section, listing the most important ideas and concepts presented. It can be used as a checklist for system design or as an index to the text when facing a difficult problem.

Appendix B details the mathematical assumptions behind various forms of rise time measurement. This section helps relate results given in this book to other sources and standards of nomenclature.

Appendix C lists standard formulas for computing the resistance, capacitance, and inductance of physical structures. These formulas have been implemented in MathCad and are available from the authors in magnetic form.

#### KNOWLEDGMENTS

Many people have contributed to this book, and we would like to thank them all. To our teachers, employers, fellow workers, clients, customers, and students, we thank you for motivating us to learn, for showing us problems we could not solve, and for occasionally humbling us when we acted like we knew too much.

The authors would like to thank individually the following people for the generous contributions they have made to the writing of this book: For meticulously reviewing the text and for offering many, many good suggestions we thank Dan Nitzan, Jim Pomerene, Joel Cyprus, Ernie Kim, Tim Ryan, and Charlie Adams.

For her efficient and cheerful assistance in preparing the figures, we thank our assistant, Pamela Moore.

Dr. Johnson would like to thank the former officers and management of ROLM corporation, particularly Ken Oshman, Bob Maxfield, and Gibson Anderson for giving him a big head start in the electronics industry.

For having a profound effect on his approach to problem-solving, and on his teaching career, Martin Graham wishes to acknowledge his mentor of long ago, Professor William McLean.

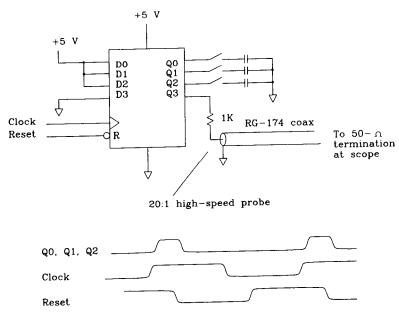

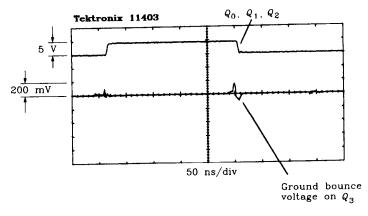

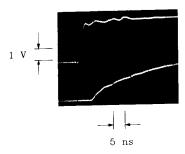

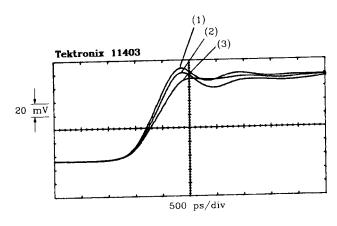

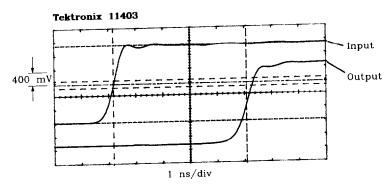

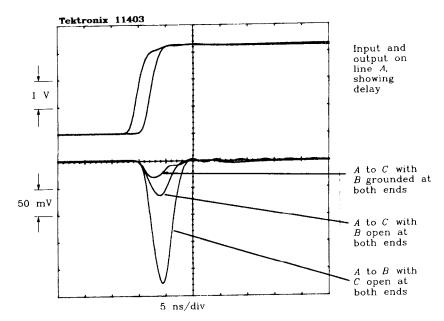

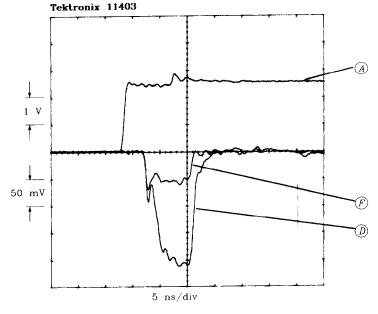

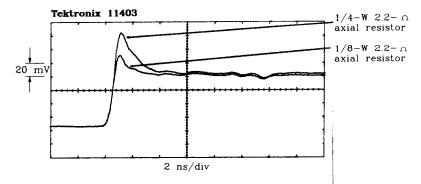

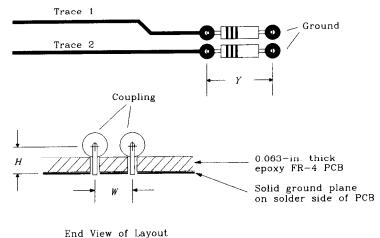

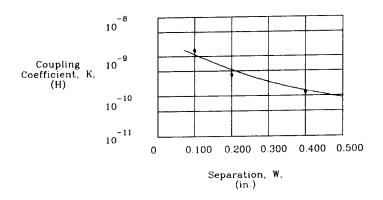

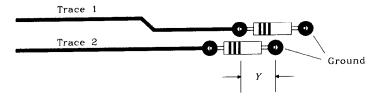

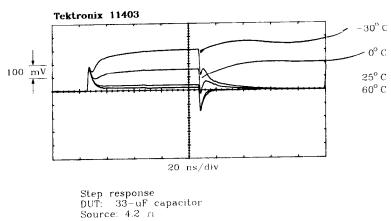

Of course, we owe a big debt of gratitude to Tektronix for loaning us a Tek 11403 digitizing oscilloscope. Their scope produced all the fine waveform displays you see in the book. Each waveform was captured, stored in memory, and then plotted directly to hard copy. Thank you, Leo Chamberlain and Jim McGoffin.

Last, and certainly not least, to our wives, Elisabeth and Selma, for their devotion and untiring support, we express our heartfelt appreciation and thanks.

Preface xi

#### **\ NOTE TO THE READER**

To those of you who will undoubtedly report the discovery of technical errors in the manuscript, thank you for your attention and for taking the time to write to us about it. The authors will personally send a certificate of appreciation to the first person to document each substantive technical error in the book. Please send your comments to:

Howard W. Johnson, Ph.D. Olympic Technology Group, Inc. 16541 Redmond Way, Suite 264 Redmond, WA 98052

# High-Speed Digital Design

# Fundamentals

High-speed digital design, in contrast to digital design at low speeds, emphasizes the behavior of passive circuit elements. These passive elements may include the wires, circuit boards, and integrated-circuit packages that make up a digital product. At low speeds, passive circuit elements are just part of a product's packaging. At higher speeds they directly affect electrical performance.

High-speed digital design studies how passive circuit elements affect signal propagation (ringing and reflections), interaction between signals (crosstalk), and interactions with the natural world (electromagnetic interference).

Let's begin our study of high-speed digital design by reviewing some relationships among frequency, time, and distance.

#### 1.1 FREQUENCY AND TIME

At low frequencies, an ordinary wire will effectively short together two circuits. This is not the case at high frequencies. At high frequencies, only a wide, flat object can short two circuits. The same wire which is so effective at low frequencies has too much inductance to function as a short at high frequencies. We might use it as a high-frequency inductor but not as a high-frequency short circuit.

Is this a common occurrence? Do circuit elements that work in one frequency range normally not work in a different frequency range? Are electrical parameters really that frequency-sensitive?

Yes. Drawn on a log-frequency scale, few electrical parameters remain constant across more than 10 or certainly 20 frequency decades. For every electrical parameter, we must consider the frequency range over which that parameter is valid.

Exploring further this idea of wide frequency ranges, let's first consider very low frequencies, corresponding to extremely long intervals of time. Then we will see what happens at very high frequencies.

A sine wave of  $10^{-12}$  Hz completes a cycle only once every 30,000 years. At  $10^{-12}$  Hz, a sine wave of transistor-transistor logic (TTL) proportions varies less than  $1\mu V$  in a day. That is a very low frequency indeed, but not quite zero.

Any experiment involving semiconductors at a frequency of  $10^{-12}$  Hz will (eventually) reveal that they do not function. It takes so long to run an experiment at  $10^{-12}$  Hz that the circuits turn to dust. Viewed on a very long time scale, integrated circuits are nothing but tiny lumps of oxidized silicon.

Given this unexpected behavior at  $10^{-12}$  Hz, what do you suppose will happen at the opposite extreme, perhaps  $10^{+12}$  Hz?

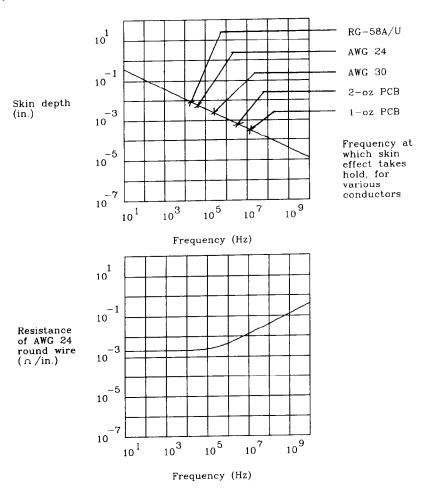

As we move radically up in frequency, to very short intervals of time, other electrical parameter changes occur. For example, the electric resistance of a short ground wire measuring 0.01  $\Omega$  at 1 kHz increases, due to the skin effect, to 1.0  $\Omega$  at 1 gHz. Not only that, it acquires 50  $\Omega$  of inductive reactance!

Big changes in performance always occur in electric circuit elements when pushed to the upper end of their operating frequency range.

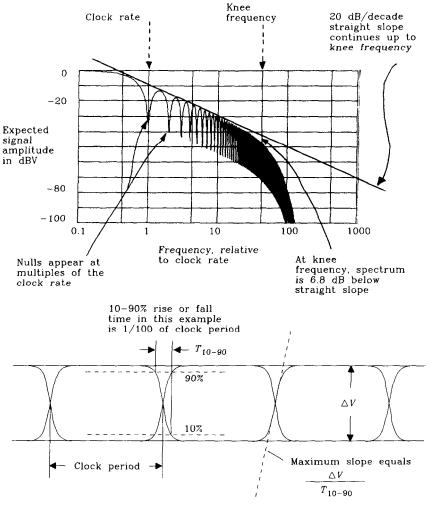

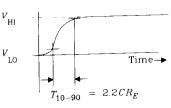

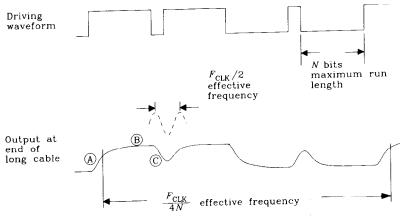

How high a range of frequencies matters for high-speed digital design? Figure 1.1 answers this question with a graph illustrating the relationship between a random digital pulse train and the important part of its frequency spectrum.

The digital signal illustrated in Figure 1.1 is the output of a D flip-flop clocked at rate  $F_{\rm clock}$ . The data value during each clock interval randomly toggles between 1 and 0. In this example the 10–90% rise and fall time, called  $T_{\rm c}$ , comprises 1% of the clock period.

The spectral power density of this signal, plotted in Figure 1.1, displays nulls at multiples of the clock rate, and an overall -20-dB/decade slope from  $F_{\rm clock}$  up to the frequency marked  $F_{\rm knee}$  (the *knee frequency*). Beyond  $F_{\rm knee}$ , the spectrum rolls off much faster than 20 dB/decade. At the knee frequency, the spectral amplitude is down by half (-6.8 dB) below the natural 20-dB/decade rolloff. The knee frequency for any digital signal is related to the rise (and fall) time of its digital edges, but not to its clock rate:

$$F_{\text{knee}} = \frac{0.5}{T_{\text{c}}} \tag{1.1}$$

where  $F_{\text{knee}}$  = frequency below which most energy in digital pulses concentrates  $T_{\text{c}}$  = pulse rise time<sup>2</sup>

Shorter rise times push  $F_{\rm knee}$  higher. Longer rise times pull  $F_{\rm knee}$  lower.

The important time domain characteristics of any digital signal are determined primarily by the signal's spectrum below  $F_{\rm knee}$ . From this principle we may deduce two important qualitative properties of digital circuits:

(1) Any circuit which has a flat frequency response up to and including  $F_{\rm knee}$  will pass a digital signal practically undistorted.

<sup>&</sup>lt;sup>1</sup>Applies to gaussian pulse shapes described in Appendix B.

<sup>&</sup>lt;sup>2</sup>For now, think of this as the 10-90% rise time. See Appendix B for an exhaustive discussion of the many ways rise time can be defined.

(2) The behavior above  $F_{\text{knee}}$  of a digital circuit will have little effect on how it processes digital signals.

Note that  $F_{\rm knee}$  is defined only by the signal rise time and bears no direct relation to other frequency domain parameters. This simple definition makes  $F_{\rm knee}$  easy to use and easy to remember.

When you apply  $F_{\rm knee}$ , keep in mind that it is an imprecise measure of spectral content. Used as a guidepost,  $F_{\rm knee}$  can help classify frequency-sensitive effects as totally insignificant, merely worrisome, or completely devastating. For most digital problems, that is exactly what we wish to know.

Figure 1.1 Expected spectral power density of a random digital waveform.

Of course,  $F_{\rm knee}$  has limitations.  $F_{\rm knee}$  cannot make precise predictions about system behavior. It doesn't even define precisely how to measure rise time! It is no substitute for full-blown Fourier analysis. It can't predict electromagnetic emissions, whose properties depend on the detailed spectral behavior at frequencies well above  $F_{\rm knee}$ .

At the same time, for digital signals,  $F_{\rm knee}$  quickly relates time to frequency in a practical and useful manner. We will use  $F_{\rm knee}$  throughout this book as the practical upper bound on the spectral content of digital signals. Appendix B contains additional information, for those interested, about various measures of rise time and frequency.

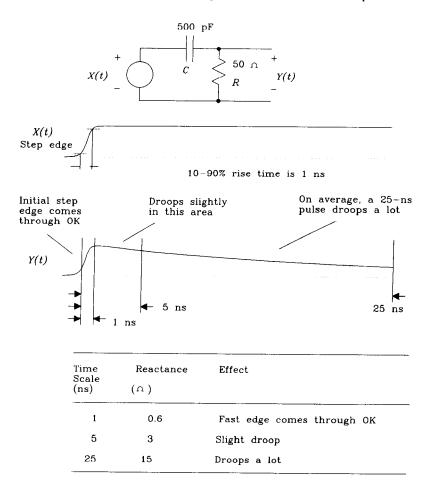

Referring back to deduction (1) above, if a system has a nonflat frequency response below  $F_{\text{knee}}$ , how will it distort a digital signal? Here is an example.

We know the response of a circuit at high frequencies affects its processing of short-time events (like a rise time). The response of a circuit at low frequencies affects its

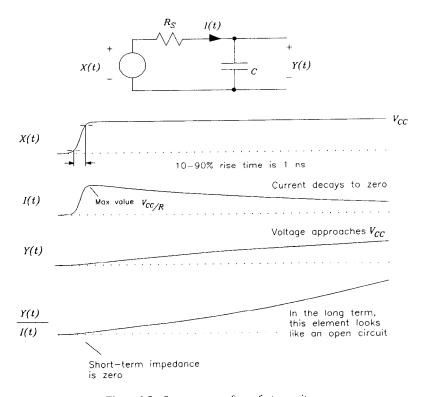

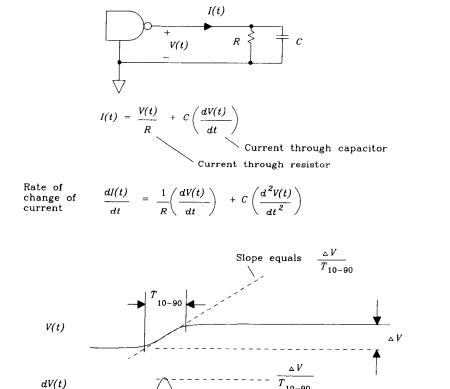

Figure 1.2 Time domain analysis of a simple RC filter.

processing of longer-term events (such as a long, steady pulse). Figure 1.2 shows a circuit having different characteristics at high and low frequencies. This circuit passes high-frequency events (the rising edge) but does not pass low-frequency events (the long, steady part).

Let's start our analysis of Figure 1.2 at one particular frequency:  $F_{\text{knee}}$ . At the frequency  $F_{\text{knee}}$ , capacitor C has a reactance (i.e., impedance magnitude) of  $1/C2\pi F_{\text{knee}}$ .

We can calculate the reactance using this formula or substitute rise time for  $F_{\text{knee}}$ :

$$X_C = \frac{1}{2\pi F_{knee} C} = \frac{T_r}{\pi C} = 0.6\Omega$$

[1.2]

where  $T_r$  = rise time of step input, s

$F_{\text{knee}}$  = highest frequency in step input, Hz C = capacitance. F

Equation 1.2 shows how to estimate the reactance of a capacitor using either the knee frequency or rise time.

A 0.6- $\Omega$  reactance acts as a virtual short in the circuit in Figure 1.2. The full amplitude of the leading edge, corresponding to a frequency of  $F_{\rm knee}$ , will come blasting straight through the capacitor.

Over a time interval of 25 ns, corresponding roughly to a frequency of 20 MHz, the capacitive reactance increases to 15  $\Omega$ , causing the coupled signal to droop noticeably.

#### POINTS TO REMEMBER:

The response of a circuit at high frequencies affects its processing of short-time events.

The response of a circuit at low frequencies affects its processing of long-term events.

Most energy in digital pulses concentrates below the knee frequency:

$$F_{\rm knee} = \frac{0.5}{T_c}$$

The behavior of a circuit at the knee frequency determines its processing of a step edge.

The behavior of a circuit at frequencies above  $F_{\rm knee}$  hardly affects digital performance.

6 Fundamentals Chap. 1

#### 1.2 TIME AND DISTANCE

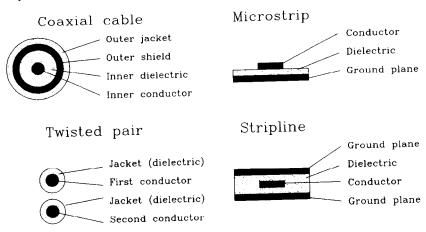

Electrical signals in conducting wires, or conducting circuit traces, propagate at a speed dependent on the surrounding medium. Propagation delay is measured in units of picoseconds per inch. Propagation delay is the inverse of propagation velocity (also called propagation speed), which is measured in inches per picosecond.

**TABLE 1.1** PROPAGATION DELAY OF ELECTROMAGNETIC FIELDS IN VARIOUS MEDIA

| Medium                    | Delay<br>(ps/in.) | Dielectric constant |

|---------------------------|-------------------|---------------------|

| Air (radio waves)         | 85                | 1.0                 |

| Coax cable (75% velocity) | 113               | 1.8                 |

| Coax cable (66% velocity) | 129               | 2.3                 |

| FR4 PCB, outer trace      | 140-180           | 2.8-4.5             |

| FR4 PCB, inner trace      | 180               | 4.5                 |

| Alumina PCB, inner trace  | 240-270           | 8-10                |

The propagation delay of conducting wires increases in proportion to the square root of the dielectric constant of the surrounding medium. Manufacturers of coaxial cable often use dielectric insulators made of foam or ribbed material to reduce the effective dielectric constant inside the cable, thus lowering the propagation delay and simultaneously lowering dielectric losses. The difference between the two coax cables listed in Table 1.1 is their dielectric insulation.

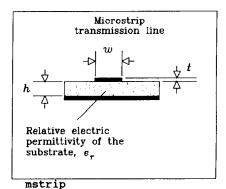

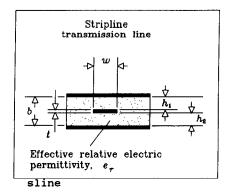

The delay per inch for printed circuit board traces depends on both the dielectric constant of the printed circuit board material and the trace geometry. Popular FR-4 printed circuit board material has a dielectric constant at low frequencies of about  $4.7\pm20\%$ , which deteriorates at high frequencies to 4.5. For propagation delay calculations, use the high-frequency value of 4.5.

Trace geometry determines whether the electric field stays in the board or goes into the air. When the electric field stays in the board, the effective dielectric constant is bigger and signals propagate more slowly. The electric field surrounding a circuit trace encapsulated between two ground planes stays completely inside the board, yielding an effective dielectric constant, for typical FR-4 printed circuit board material, of 4.5. Traces laid on the outside surface of the printed circuit board (outer traces) share their electric field between the air on one side and the FR-4 material on the other, yielding an effective dielectric about halfway between 1 and 4.5. Outer-layer PCB traces are always faster than inner traces.

Alumina is a ceramic material used for constructing very dense circuit boards (up to 50 layers). It has the advantage of a low coefficient of thermal expansion and machines easily in very thin layers, but it is very expensive to manufacture. Microwave engineers like the slow propagation velocity (large delay) of alumina circuits because it shrinks the size of their resonant structures.

#### POINTS TO REMEMBER:

Propagation delay is proportional to the square root of the dielectric constant.

The propagation delay of signals traveling in air is 85 ps/in. Outer-layer PCB traces are always faster than inner traces.

#### 1.3 LUMPED VERSUS DISTRIBUTED SYSTEMS

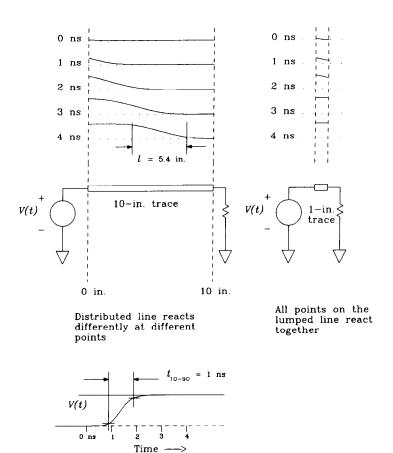

The response of any system of conductors to an incoming signal depends greatly on whether the system is smaller than the effective length of the fastest electrical feature in the signal, or vice versa.

The effective length of an electrical feature, like a rising edge, depends on the time duration of the feature and its propagation delay. For example, let's analyze the rising edge of a 10KH ECL signal. These gates have a rise time of approximately 1.0 ns. This rising edge, when propagating along an inner trace of an FR-4 printed circuit board, has a length of 5.6 in.:

$$l = \frac{T_r}{D} \tag{1.3}$$

where l = length of rising edge, in.

$T_r$  = rise time, ps

D = delay, ps/in.

Figure 1.3 depicts a series of snapshots of the electric potential along a straight trace 10 in. long. A rising edge of 1-ns duration impinges on the left end of the trace. Evidently, as the pulse propagates along the trace, the potential is not uniform at all points. The reaction of this system to the incoming pulse is distributed along the trace, which we label a *distributed system*. The snapshot taken at 4 ns shows the physical length of this rising edge is 5.4 in.

Systems physically small enough for all points to react together with a uniform potential are called *lumped systems*. Figure 1.3 illustrates the response of a 1-in. trace, carrying the same 1-ns rising edge, which behaves as a lumped system. The voltage on every part of this line is (almost) uniform at all times.

The classification of a system as distributed or lumped depends on the rise time of the signals flowing through it. The distinguishing characteristic is the ratio of system size to rise-time size. For printed circuit board traces, point-to-point wiring, and bus structures if the wiring is shorter than one-sixth of the effective length of the rising edges, the circuit behaves mostly in a lumped fashion.<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>Some authors use  $l/\sqrt{2\pi}$ ; others use l/4. The idea is that small structures are lumped circuits, while big ones are distributed.

Figure 1.3 Snapshots in time of the electric potential on distributed and lumped transmission lines.

# POINTS TO REMEMBER: Length of rising edge $I = \frac{\text{Rise time (ps)}}{\text{Delay (ps/in.)}}$ Circuits smaller than #6 are lumped circuits.

## .4 A NOTE ABOUT 3-dB AND RMS FREQUENCIES

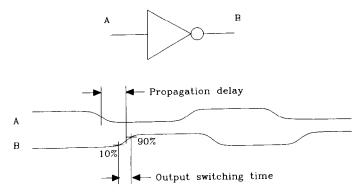

When translating specifications from the analog world to the digital world, one often must convert from frequency response to rise time.

For example, oscilloscope manufacturers quote a maximum operating bandwidth for each vertical amplifier and a corresponding maximum bandwidth for each probe. Depending on the manufacturer, they may quote a 3-dB bandwidth or an RMS (noise equivalent) bandwidth. In either case, the conversions between bandwidth and rise time will depend on the exact shape of the scope's frequency response curve.

Fortunately, we do not often need to compute an exact rise time. For the purposes of this book, we may devise an approximate relation that is easy to apply while ignoring complicated details of the exact frequency response shape. Appendix B provides justification for this approach, comparing exact calculations for several different pulse types.

The conversions listed below assume we are translating from frequency response to a 10–90% rise time. As explained in Appendix B, for the accuracy we require in diagnosing and fixing digital problems it hardly matters whether we define rise time using the 10–90% rise time, inverse of the slope at the center of the pulse, or standard deviation method.

$$F_{\rm 3dB} \approx \frac{K}{T_r} \tag{1.5}$$

$$T_r \approx \frac{K}{F_{3\text{dB}}} \tag{1.6}$$

where  $F_{3dB}$  = frequency at which impulse response rolls off by 3 dB

$T_r$  = pulse rise time (10–90%)

K =constant of proportionality depending on exact pulse shape;

K = 0.338 for gaussian pulses; K = 0.350 for single-pole exponential decay

If we change our pulse type from gaussian to a single-pole exponential decay, the constant in Equation 1.6 changes from 0.338 to 0.350. For most digital designs, such a subtle distinction hardly matters.

Where a manufacturer quotes the RMS bandwidth, or equivalent noise bandwidth, of a subsystem, the following relation computes the 10-90% rise time of that subsystem. Here the constant K changes from 0.36 to 0.55 depending on the pulse type, a slightly more significant change than in Equation 1.6.

$$T_r \approx \frac{K}{F_{\rm RMS}}$$

[1.7]

where  $F_{RMS} = RMS$  bandwidth

$T_r = \text{rise time } (10-90\%)$

K =constant of proportionality depending on exact pulse shape;

K = 0.361 for gaussian pulses; K = 0.549 for single-pole exponential decay

<sup>&</sup>lt;sup>4</sup>The noise bandwidth of a frequency response H(f), or RMS bandwidth, is the cutoff frequency at which a box-shaped frequency response would pass the same amount of white noise energy as H(f).

When you look at a scope response to a very fast rising edge (much faster than the scope response), you can usually tell if it has a single-pole or a gaussian-type response. If the leading edge of the response has a sharp corner, suddenly taking off at a steep angle and blending into a long, sweeping tail, it is probably a single-pole response. If the pulse edge sweeps up gently, with symmetric leading and trailing edges, it is probably nearly gaussian. In between, use K = 0.45.

#### 1.5 FOUR KINDS OF REACTANCE

Four circuit concepts separate the study of high-frequency digital circuits from that of low-speed digital circuits: capacitance, inductance, mutual capacitance, and mutual inductance. These four concepts provide a rich language for describing and understanding the behavior of digital circuit elements at high speeds.

There are many ways to study capacitance and inductance. A microwave engineer studies them using Maxwell's equations. A designer of control systems uses Laplace transforms. An advocate of Spice simulations uses linear difference equations. Digital engineers use the step response.

The step response measurement shows us just what we need to see: what happens when a pulse hits a circuit element. From the step response, if we wish, we can derive a curve of impedance versus frequency for a circuit element. In that sense the step response measurement is (at least) as powerful as any frequency-domain measure of impedance.

Our investigation of capacitance and inductance will focus on the step response of circuit elements.

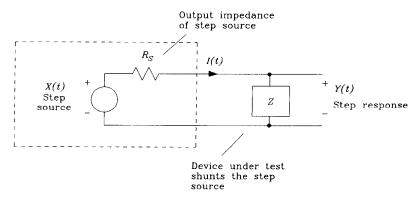

Figure 1.4 illustrates a classic step response measurement for a two-terminal device. In this figure, we use a step source having an output impedance of  $R_S$  ohms. The step source is shunted by the device under test, across which we measure the voltage response. In practical measurements, the step input is repeated over and over again while the results are synchronously displayed on an oscilloscope.

Figure 1.4 Step response test for a two-terminal device.

With practice, anyone can learn to instantly characterize the device under test by observing the step response and using these three rules of thumb:

- (1) Resistors display a flat step response. At time zero, the output rises to a fixed value and holds steady.

- (2) Capacitors display a rising step response. At time zero, the step response starts at zero but then later rises to a full-valued output.

- (3) Inductors display a sinking step response. At time zero, the output rises instantly to full value and then later decays back toward zero.

To first order, we may characterize any circuit element according to whether, as a function of time, its step response stays constant, rises, or falls. We label these elements resistive, capacitive, and inductive, respectively.

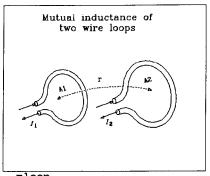

Reactive effects (both capacitance and inductance) further subdivide into ordinary and mutual categories. The ordinary varieties of capacitance and inductance describe the behavior of individual circuit elements (two-terminal devices). The mutual capacitive and inductive concepts describe how one circuit element affects another. In digital electronics, mutual capacitance or inductance usually creates unwanted crosstalk, which we strive to minimize. Plain capacitance or inductance can be a help or a hindrance, depending on the circuit application.

We will define and use a special version of step response for characterizing mutual capacitive and mutual inductive circuit elements.

Our brief study of reactive concepts considers only lumped circuit elements, in this order:

- · Ordinary capacitance

- · Ordinary inductance

- Mutual capacitance

- · Mutual inductance.

#### 1.6 ORDINARY CAPACITANCE

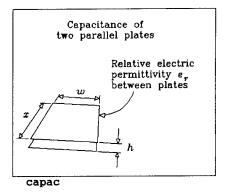

Capacitance arises wherever there are two conducting bodies charged to different electric potentials. Two bodies at different electric potentials always have an electric field between them. The energy stored in their electric field is supplied by the driving circuit. Because the driving circuit is a limited source of power, the voltage between any two bodies takes a finite amount of time to build up to a steady-state value. The reluctance of voltage to build up quickly in response to injected power, or to decay quickly, is called *capacitance*. Structures enclosing a large amount of electric flux at low voltages, like two parallel plates, have lots of capacitance.

Figure 1.5 shows idealized current and voltage waveforms for a capacitor driven by a  $30-\Omega$  source.<sup>5</sup> The step response of a capacitor grows as a function of time. When a

<sup>&</sup>lt;sup>5</sup>The 30- $\Omega$  source is an approximation to the drive capability of a standard TTL output.

12 Fundamentals Chap. 1

Figure 1.5 Step response of a perfect capacitor.

voltage step is first applied, lots of power flows into the capacitor to build up its electric field. The initial current into the capacitor is quite high and the ratio Y(t)/I(t) very low. At short time scales, the capacitor looks like a short circuit.

Over time, the ratio Y(t)/I(t) gets bigger. Eventually, the current falls to near zero and the capacitor starts to look like an open circuit. Finally, after the electric field surrounding the capacitor is fully formed, only a small leakage current flows as a result of the imperfect insulating qualities of the dielectric medium between the capacitor plates. The ratio Y(t)/I(t) then is extremely high.

The step response of some circuit elements displays a capacitive character when viewed at one time scale, and an inductive behavior at a different time scale, or vice versa. For example, the mounting leads on capacitors commonly have enough inductance to cause the overall component to look inductive at very high frequencies. The step response of such a capacitor shows a tiny pulse of perhaps a few hundred picoseconds at time zero (corresponding to the inductance), then a drop to zero, and then a normal upward-moving capacitive ramp.

If the rise time of the step source is too slow, the output trace won't show the inductive spike. Because the spike is so short, it is also easy to miss if the scope time base

<sup>&</sup>lt;sup>6</sup>Equivalently, the element behaves differently at different frequencies. Our focus here is on time domain response.

is set for too slow a sweep. It is interesting to contemplate the idea that by adjusting the rise time and setting the time base sweep, we can cause the step response measurement to emphasize the character of a circuit element in a particular frequency range. Roughly speaking, if the step rise time is  $T_r$ , the step response near time zero is related to the impedance magnitude of the circuit element near frequency  $F_A$ :

$$F_{\rm A} \approx \frac{0.5}{T_{\rm c}} \tag{1.8}$$

where  $T_r$  = rise time of step source  $F_A$  = approximate analysis frequency

By visually averaging the step response over a time interval, we can estimate the impedance magnitude at lower frequencies. Use Equation 1.8 to compute the approximate analysis frequency that corresponds to an averaging interval of  $T_r$ .

The final value of the step response indicates the impedance magnitude at DC.

With a step rise time of  $T_r$ , we cannot infer much about the behavior of the component at frequencies greater than  $F_A$ . Make sure your step source is fast enough to reveal what you want to see.

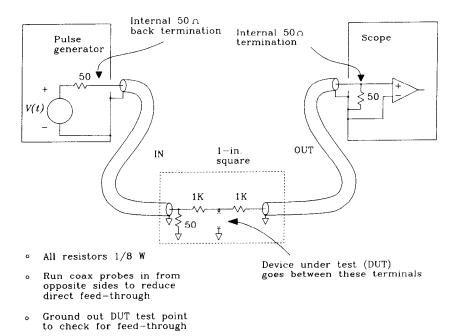

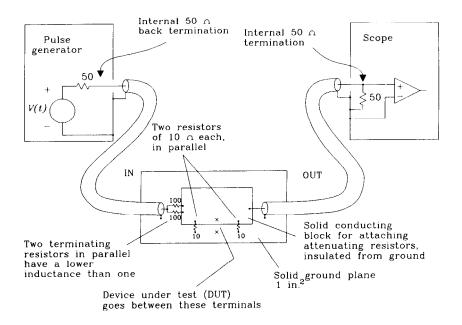

Figure 1.6 shows a measurement setup ideal for characterizing capacitors of a few picofarads over a time interval of nanoseconds. This arrangement is ideal for characterizing the capacitance of circuit traces, gate inputs, bypass capacitors, and other common digital circuit elements. This method drives the capacitor under test with a known resis-

Figure 1.6 A 500- $\Omega$  lab setup for measuring capacitance.

14 Fundamentals Chap. 1

tance. By measuring the rise time of the resulting waveform, we can infer a value for the capacitance. In comparison to techniques used at audio frequencies, this setup is very complicated. The complication follows from the difficulty of containing and directing electromagnetic field energy at high frequencies. The coaxial cables are used to direct the test signals and measured results into and out of a solid ground plane area no more than 1 in.<sup>2</sup> where the actual measurement takes place. Limiting the measurement footprint to 1 in.<sup>2</sup> ensures that the circuit will behave in a lumped fashion.

#### Example 1.1: Measurement of a Small Capacitance to Ground

The device under test (DUT) in this example (Figure 1.6) is a parallel plate capacitor, 0.5 in.  $\times$  0.75 in., printed in  $1\frac{1}{2}$ -oz copper on an epoxy FR-4 printed circuit board, nominally 0.008 in. above a solid ground plane. This structure forms a capacitor with extremely low parasitic series inductance.

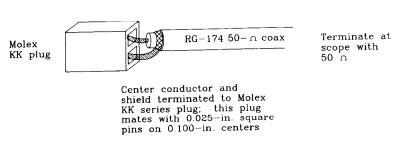

The measurement setup consists of two RG-174 coaxial cables, IN and OUT. The IN cable, terminated with 50  $\Omega$  to ground, includes a 1K drive resistor connected from the terminated output to the device under test. The 1K resistor isolates the signal source from the device under test, providing to the source a constant terminating impedance regardless of the impedance of the DUT. Isolation ensures consistent source rise time and amplitude performance regardless of the DUT load impedance.

The source pulse generator provides signals of similar amplitude and rise time as that expected in the actual circuit. When measuring passive components, the DC offset of the pulse generator does not much matter. On the other hand, when measuring gate inputs, always adjust the pulse source to span the input switching range and apply power to the gate under test. That biases the gate into its operating range for the test. Gates requiring lots of input drive current may need source resistors smaller than  $1K\Omega$ .

If your signal generator has a  $50-\Omega$  back-termination feature, engage it to reduce reflections on the IN cable. This feature inserts  $50~\Omega$  in series with the signal generator output, reducing reflections back and forth along the source cable between the unavoidable slight mismatch at the test jig and the output impedance of the signal source. Using the back termination, unwanted reflections from your source signal now are attenuated first when they bounce off the test jig and a second time as they bounce off the back termination resistor in the signal source on their return path to your measuring apparatus. The back termination reduces the available source drive amplitude by half but improves the system step response.

The OUT cable connects separately through 1K  $\Omega$  to the circuit under test, running to an oscilloscope input internally terminated with 50  $\Omega$ . The 1K resistor acts as a 21:1 probe. The advantages of this sensing arrangement are detailed later in this book in the section on oscilloscope probing. Both IN and OUT cables are 3 ft long.<sup>7</sup>

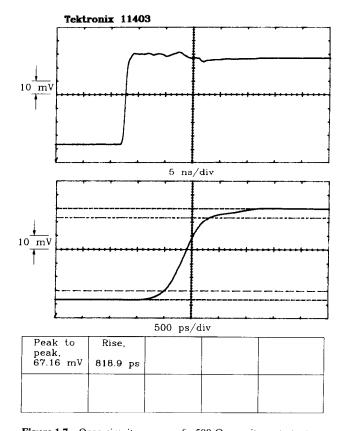

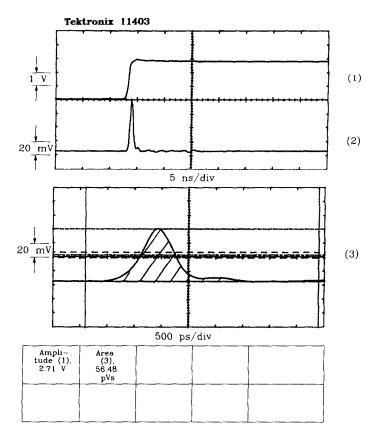

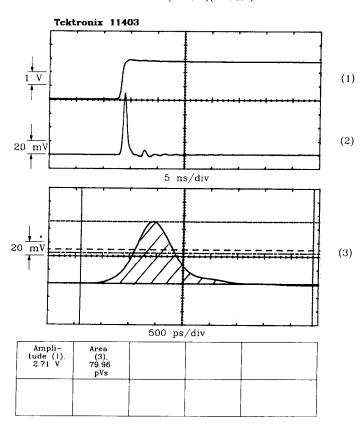

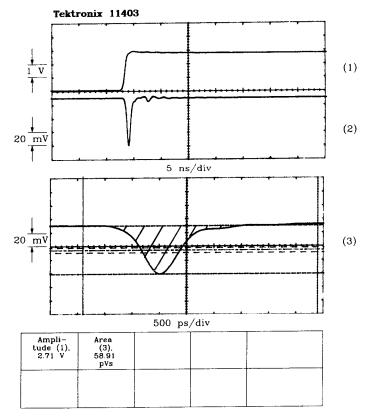

The open-circuit response of this probe, when driven by a 2.6-V step input from the source with the DUT disconnected, appears in Figure 1.7. The top trace is recorded at 5 ns/division, and the bottom trace is an exploded view of the same signal at 500 ps/division.

The Tektronix 11403 scope used to record this waveform automatically computes a 10-90% rise time of 818 ps. The nominal step amplitude is 63 mV (the scope measures a

<sup>&</sup>lt;sup>7</sup>Longer cables can be an advantage, in that reflections occur so late that they do not show on the scope. The disadvantage to longer cables is that they introduce more signal dispersion. At some length the cable response begins to deteriorate the observable rise time. In Figure 1.7 reflection effects from the 3-ft cables show up about 8 ns into the picture.

Figure 1.7 Open-circuit response of a  $500-\Omega$  capacitance test setup.

*peak* of 67 mV). Note that the measured step amplitude is  $\frac{1}{21}$  the amplitude at the DUT of 1.3 V, which is in turn half the source drive voltage.

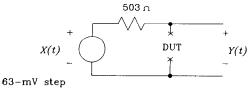

The Thevinen equivalent circuit for this test arrangement, as shown in Figure 1.8, includes the aggregate system rise time lumped into the source. It matters not whether the signal source or the scope contributes more to the slowness of the observed rise time. Any reasonable combination of source and scope having a similar open-circuit rise time will behave similarly under the influence of the DUT. It matters only that we know the aggregate rise time of the source scope combination. When measuring passive components, it similarly matters only that we know the observed step amplitude, details of the actual voltage at the DUT and the probe attenuation ratio being unimportant.

820-ps 10-90% rise time

Figure 1.8 The venin equivalent of a 500- $\Omega$  capacitance test setup.

The source impedance is 503  $\Omega$ , as measured at the DUT terminals using an ohmmeter with the pulse source turned off but the back termination to 50  $\Omega$  still connected. This 503  $\Omega$  is the parallel combination of the 1K drive resistor and the 1K sense resistor.

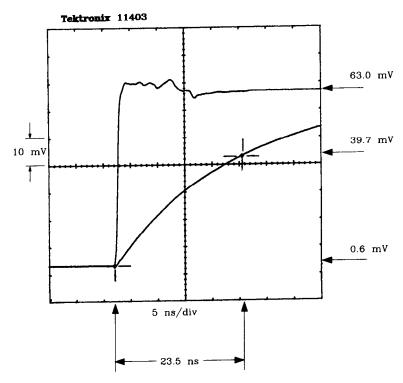

With the DUT connected, the observed voltage displays a capacitive character, starting low and then rising (see Figure 1.9). A stored copy of the original drive waveform is superimposed on this picture for reference. Over the range of time scales observable with this probe, from 800 ps (the aggregate source-probe combination rise time) to 40 ns (the length of trace appearing in the scope photo) the DUT appears perfectly capacitive.

Cursors in Figure 1.9 mark the 63% point along the rise time where we can read off the RC time constant of 23.5 ns. Knowing the drive resistance of 503  $\Omega$ , we can compute the capacitance of the DUT using the relation  $C = \tau/R$ :

$$C = \frac{23.5 \times 10^{-09} \,\mathrm{s}}{503 \,\Omega} = 46.7 \,\mathrm{pF}$$

[1.9]

We can use the relationship between rise time and frequency to derive a rough idea of the reactance presented by a capacitor to the leading edge of a digital waveform. This

Figure 1.9 Finding a time constant using the 63% method.

<sup>&</sup>lt;sup>8</sup>In one time constant, a rising edge progresses to 63% of its final value, and a falling edge deteriorates to 37% of its initial value.

approach is very useful when considering the distortion introduced in a digital waveform by a capacitive load.

$$X_C = \frac{T_r}{\pi C}$$

[1.10]

The capacitor in Example 1.1 has a reactance of 20.44  $\Omega$  to a rising edge of 3 ns. We therefore predict it will significantly distort (by slowing down) a 3-ns rising edge from a TTL driver having an output impedance of 30  $\Omega$ .

The current through a capacitor at any point in time is always related to the rise time of the voltage across it according to the general formula

$$I_{\text{capacitor}} = C \frac{dV_{\text{capacitor}}}{dt}$$

[1.11]

Equation 1.11 will help us later when calculating crosstalk due to capacitance between circuits.

#### POINT TO REMEMBER:

A capacitance test jig is easy to build using a pulse source and an oscilloscope.

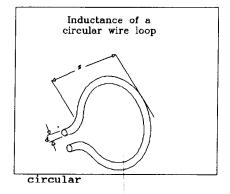

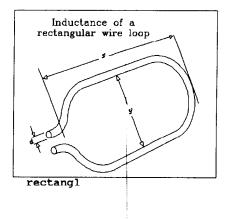

## 1.7 ORDINARY INDUCTANCE

Inductance arises wherever there is electric current. Electric current creates a magnetic field, with the energy stored in the magnetic field supplied by some driving circuit. Because any driving circuit is a limited source of power, current always takes a finite amount of time to build up to a steady-state value. The reluctance of current to build up quickly, or to decay quickly, is called *inductance*.

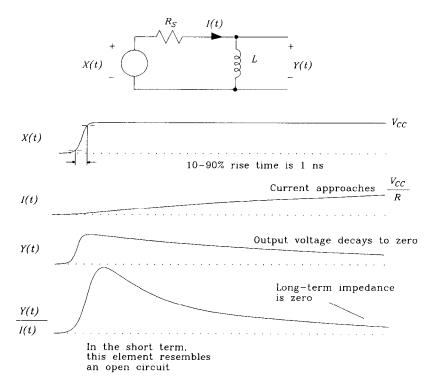

Figure 1.10 shows idealized current and voltage waveforms for an inductor driven by a 30- $\Omega$  source. The step response of an inductor shrinks as a function of time. When a voltage step is first applied, almost no current flows, making the ratio Y(t)/I(t) very high. At short time scales, the inductor looks like an open circuit.

Over time, the ratio Y(t)/I(t) decays. Eventually, the voltage drops to near zero and the inductor starts to look like a short circuit. Later, after the magnetic field surrounding the inductor is fully formed, the current is limited only by the DC resistance of the inductor. The ratio Y(t)/I(t) is then extremely low.

Figure 1.11 shows a measurement setup optimized for characterizing inductors of a few nanohenries. This arrangement is ideal for measuring the inductance of ground traces or short lengths of connecting wiring.

Figure 1.10 Instantaneous resistance of a perfect inductor.

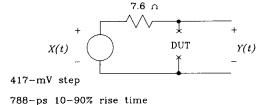

**Figure 1.11** A 7.6- $\Omega$  lab setup for measuring inductance.

#### **EXAMPLE 1.2: Measurement of a Small Inductance to Ground**

The device under test (DUT) in this example (Figure 1.11) is a short 1-in. circuit trace printed in  $1\frac{1}{2}$ -oz copper on an epoxy FR-4 printed circuit board. The trace nominally rides 0.008 in. above a solid ground plane and is 0.010 in. wide. The far end of the trace is shorted to ground with a 0.035-in.- diameter via. This structure has a parasitic capacitance to ground of 2 pF when open-circuited, and half that when the far end is shorted. The calculated inductance is about 9 nH.

We plan to characterize this circuit using an 800-ps rise time. First check that the parasitic capacitive reactance at that speed is much larger than the inductive reactance we wish to see.

$$X_C = \frac{T_r}{\pi C} = 254 \,\Omega \tag{1.12}$$

$$X_L = \frac{\pi L}{T} = 35 \ \Omega \tag{1.13}$$

The capacitive reactance, which appears in parallel with our measurement, is eight times bigger than the expected inductive reactance. The effect of this capacitance will be to increase our observed value of L/R by about 12%.

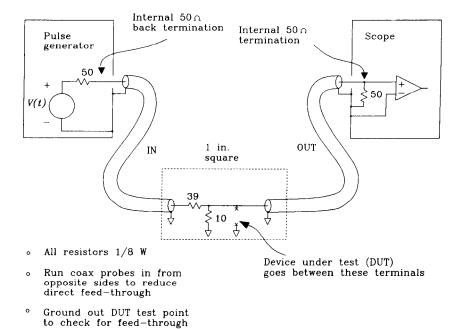

The measurement setup consists of two RG-174 coaxial cables, IN and OUT. The IN cable, terminated in a total of 49  $\Omega$  to ground, includes a tap of 10  $\Omega$  for driving the DUT. In this jig the source is not as well isolated from the DUT as in the capacitance test jig. The terminating impedance seen by the source varies from 39 to 49  $\Omega$  under various DUT load conditions. <sup>10</sup> Because we expect reflections off the mismatch at the DUT, do not forget to back-terminate your pulse generator.

The generator is adjusted for no DC offset. The inductor would short out any DC offset anyway.

The source impedance is 7.6  $\Omega$  as measured at the DUT with the source turned off but the back termination connected. This is a parallel combination of the 50 + 39- $\Omega$  source impedance, the 10- $\Omega$  tap resistor, and the 50- $\Omega$  probe impedance.

We have arranged for a low source impedance at the DUT to exaggerate the L/R decay time. Had we used a test jig with a 500- $\Omega$  Thevenin equivalent source resistance, the expected L/R time would be only 0.018 ns. With a 7.6- $\Omega$  source we expect a 1.2-ns L/R decay constant.

The OUT cable connects directly to the DUT in this experiment and runs to an oscilloscope input internally terminated with 50  $\Omega$ . Both IN and OUT cables are 3 ft long.

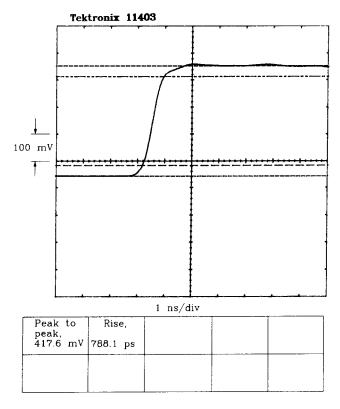

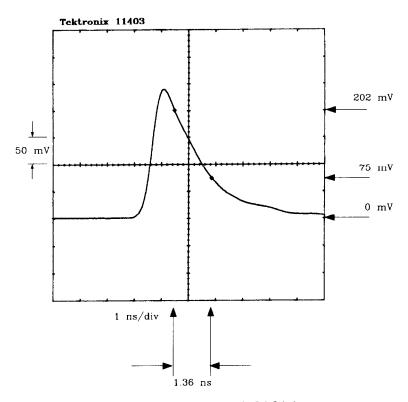

The open-circuit response of this 7.6- $\Omega$  test setup, when driven by a 2.4-V step input, appears in Figure 1.12. The scope automatically computes a 10–90% rise time of 788 ps. The step amplitude is 417 mV. The probe is a 1:1 arrangement, so the voltage at the DUT is actually 417 mV.

Figure 1.13 shows the Thevenin equivalent circuit of this 7.6- $\Omega$  test setup.

<sup>9</sup>For those familiar with short transmission line theory, according to the pi model (C+L+C) for a short transmission line shorting the far end just shorts out one of the two capacitors. The result is a tank circuit composed of the full inductance and half the open circuit capacitance.

<sup>10</sup>Because the short-term impedance of the inductor is high, the best choice for the terminating network is 39 and 10  $\Omega$ , giving a 49- $\Omega$  initial value. This terminates the initial rising step edge with 49  $\Omega$ . Were we measuring the low-inductance capacitor of Example 1.1, the best choice would be 50 and 10 ohms, because the short-term impedance of a capacitor is initially zero.

20 Fundamentals Chap. 1

Figure 1.12 Open-circuit response of a 7.6- $\Omega$  inductance test setup.

**Figure 1.13** Thevenin equivalent of a 7.6- $\Omega$  inductance test setup.

With the DUT connected (Figure 1.14) the observed voltage manifests an inductive character, rising quickly along with the input signal and then decaying later toward zero. Over the range of time scales observable with this setup, from 800 ps (the aggregate source-scope combination rise time) to 7 ns (the length of trace appearing in the scope photo), the DUT is inductive. The exponential decay time is 1.36 ns as measured by the two cursors carefully positioned at voltages separated by a multiplicative factor of e.

From the measured decay constant, using the relation  $L = R\tau$ , we may compute the inductance of the DUT:

$$L = (1.4 \times 10^{-09})(7.6 \Omega) = 10.6 \text{ nH}$$

[1.14]

Figure 1.14 Decaying exponential response of a 7.6- $\Omega$  inductance test setup.

We can use the relationship between rise time and frequency to derive a rough idea of the reactance presented by an inductor to the leading edge of a digital waveform. This approach is very useful when considering the ground bounce introduced in a poor ground connection by a parasitic series inductance.

$$X_L = \frac{\pi L}{T_r} \tag{1.15}$$

The inductor of Example 1.2, a trace 1 in. long, has a reactance of 9.4  $\Omega$  to a rising edge of 3 ns. If this trace is used to ground a 50- $\Omega$  terminator for 3-ns rising edges, the composite termination value will be off by 20%. If this trace is used to ground a bank of eight 50- $\Omega$  terminators, the parallel impedance of eight terminators ( $\frac{50}{8} = 6 \Omega$ ) is actually less than the trace impedance. If all eight terminated lines switch simultaneously, the terminating bank won't work.

The voltage across an inductor at any point in time is always related to the rise time of the current through it according to the general formula

$$V_{\text{inductor}} = L \frac{dI_{\text{inductor}}}{dt}$$

[1.16]

We will use Equation 1.16 later when calculating crosstalk due to inductance between circuits.

On the subject of what does and doesn't work as a short circuit, consider two common ways of shorting a digital line to ground: a knife blade and a pair of needle-nosed pliers.

During the debugging process, one often needs to short a signal to ground in order to test a hypothesis about how the circuit functions (or doesn't function). If the shorting instrument has too high an inductance, narrow pulses will slip through unshorted. Clock lines and asynchronous interrupt lines are especially susceptible to this narrow-pulse problem.

The inductance of a knife blade when used to short together two circuit nodes located 0.300 in. apart is on the order of a couple of nanohenries. To a 1-ns rising edge, the knife blade presents an impedance magnitude of about 6  $\Omega$  (Equation 1.15).

The inductance of a pair of needle-nosed pliers used to short the same nodes (one plier tip on each node) is on the order of 10-20 nH. The trip up one leg of the pliers, through the joint, and back down the other side introduces an order of magnitude more inductance than a small knife blade. To the same 1-ns rising edge, the pliers present an impedance magnitude of at least  $30~\Omega$ . Thirty ohms is not low enough to ground out a short TTL pulse. Enough said.

## .8 A BETTER METHOD FOR ESTIMATING DECAY TIME

In the inductance test jig, the ratio of the expected characteristic decay time  $T_{L/R}$  to the open-circuit rise time of the test setup  $T_{open}$  is not very great:

$$\frac{T_{L/R}}{T_{\text{open}}} = \frac{1 \times 10^{-09}}{0.8 \times 10^{-09}} = 1.2$$

[1.17]

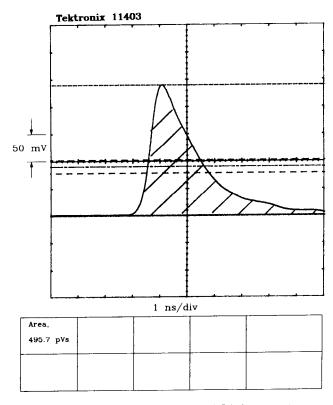

This low ratio means that before the initial step rise completes, the test waveform has already begun to decay. The measured output waveform is not a clean exponential shape but is more complex. Careful observation of the peak amplitude in Figure 1.14 reveals that it reaches a maximum of only 250 mV, compared to the open-circuit asymptote of 417 mV. This evidence suggests that the exponential time constant measured in Example 1.2 may not accurately reflect the true inductance. Were we to go further out on the waveform to measure the decay constant, away from the initial step, the actual wave would decay more exponentially. Unfortunately, we can't go much further out because parasitic coupling, reflections, and other noise make the waveform lumpy as we move toward the right of the screen.

## 1.8.1 Measuring Total Area Under a Response Curve

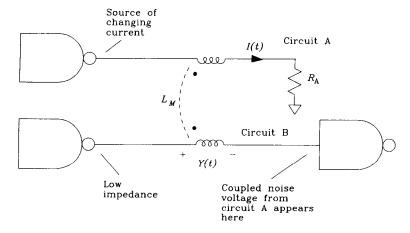

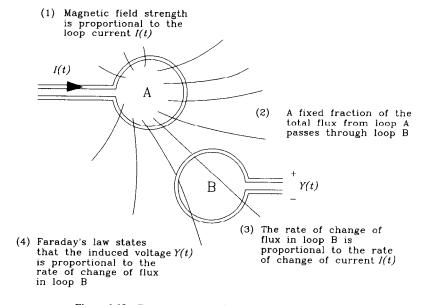

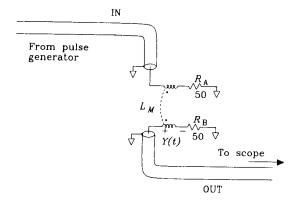

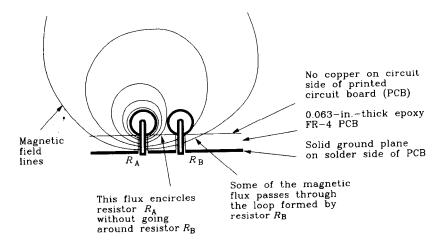

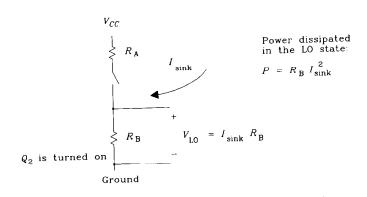

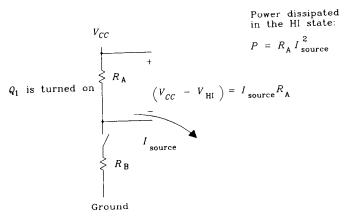

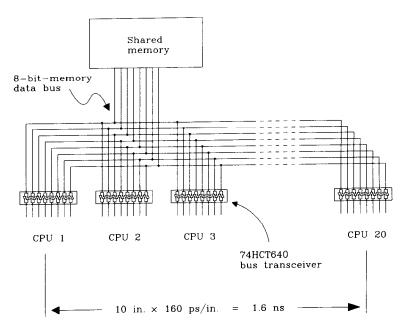

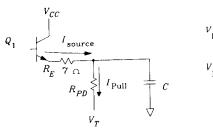

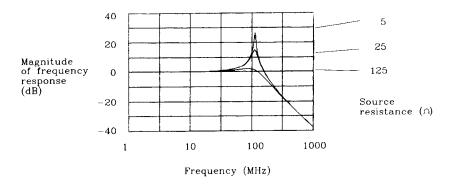

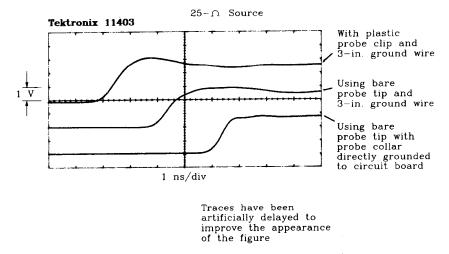

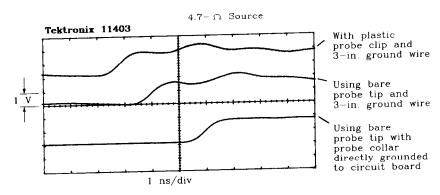

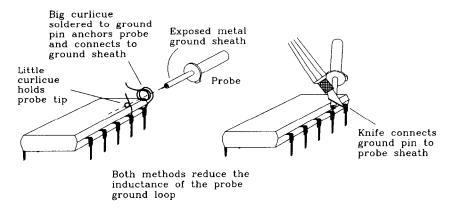

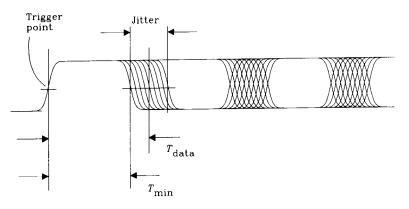

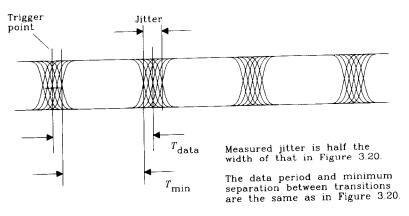

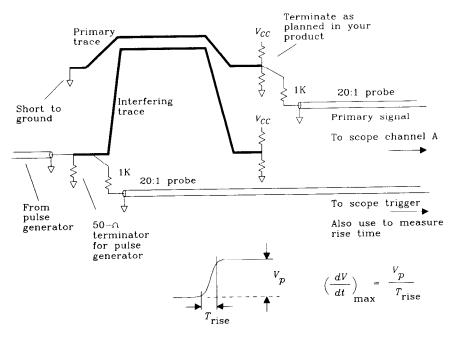

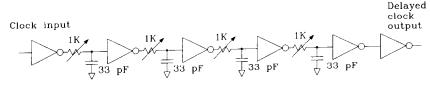

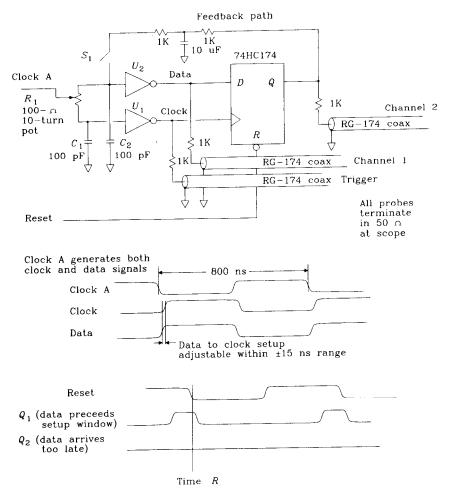

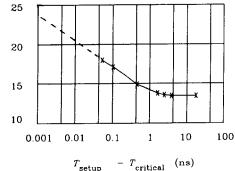

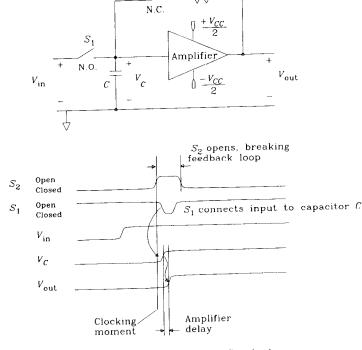

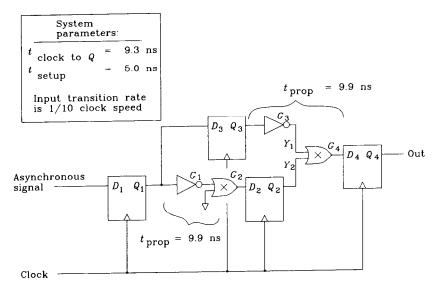

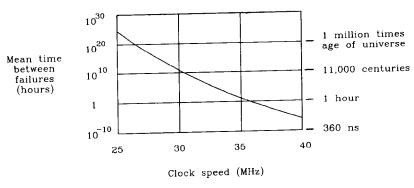

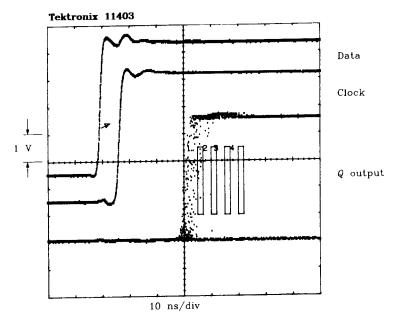

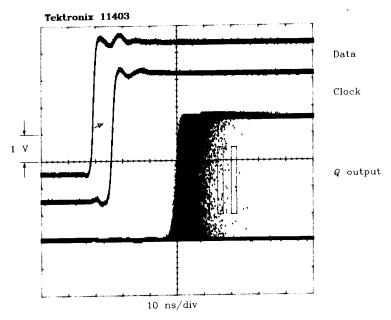

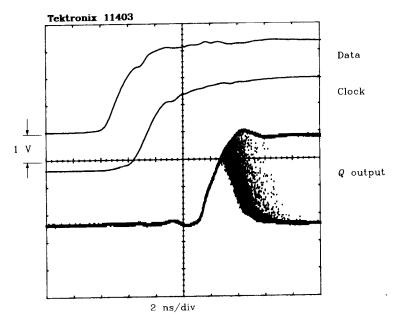

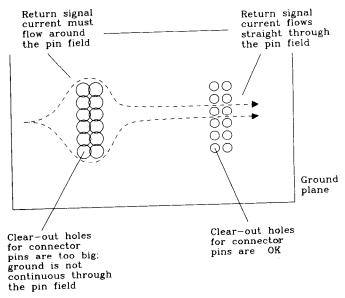

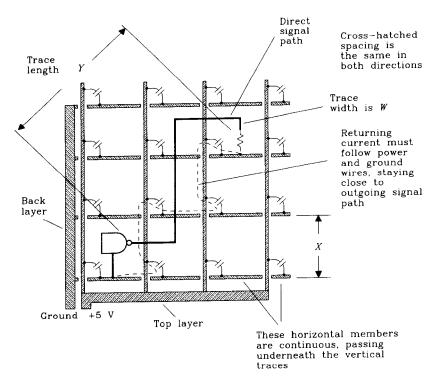

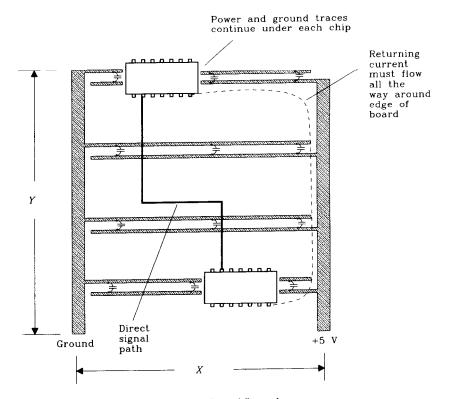

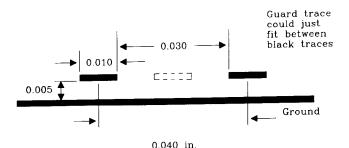

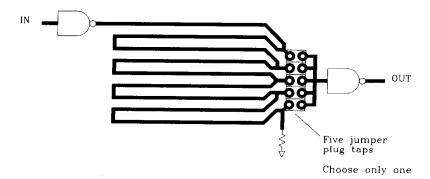

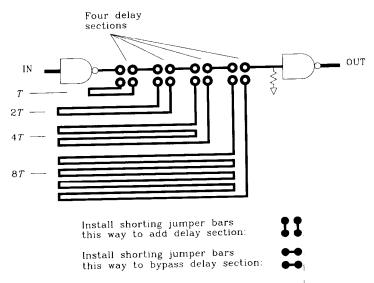

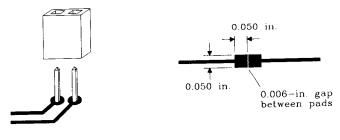

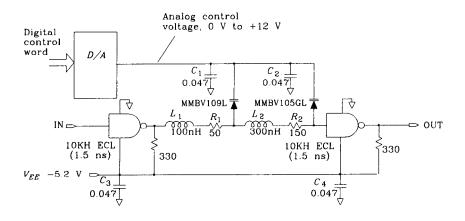

We need a more reliable way to use the shape of the curve in Figure 1.14 to estimate inductance. We would like something that considers the whole waveform, not just the